MSI 760GM-P33 – страница 3

Инструкция к Материнской Плате Amd MSI 760GM-P33

MS-7623

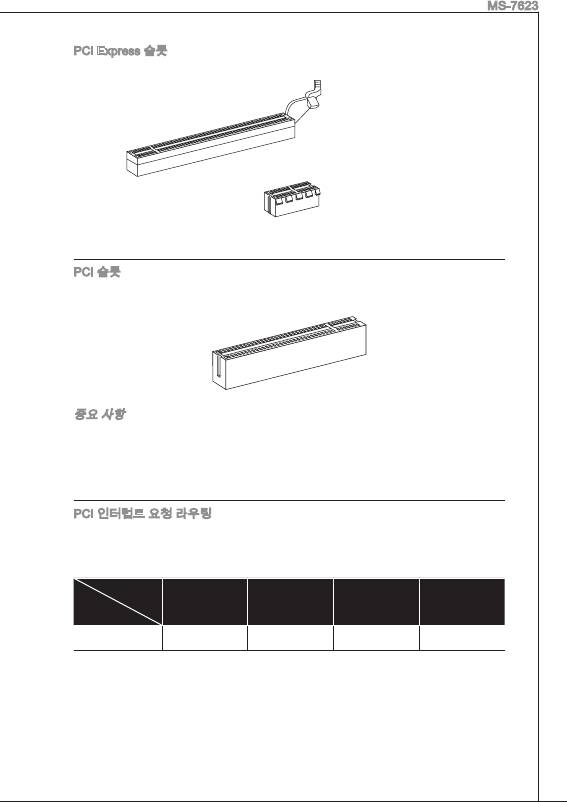

PCI Express 슬롯

PCI Express 슬롯은 PCI Express 인터페이스 확장 카드를 지원합니다.

PCI Express x16 슬롯.

PCI Express x1 슬롯.

PCI 슬롯

PCI 슬롯은 LAN 카드, SCSI 카드, USB 카드 및 PCI 규격을 준수하는 기타 애드

온 카드를 지원합니다.

중요 사항

먼저 전원 공급 장치의 플러그를 뽑으십시오. 점퍼, 스위치 또는 BIOS 구성과 같

은 확장 카드에 대해 필요한 하드웨어 및 소프트웨어 설정을 구성하려면 확장 카드

의 설명서를 읽으십시오.

PCI 인터럽트 요청 라우팅

확장 카드를 추가또는 제거하는 때 Interrupt request line의 약어인 IRQ는 I-R-Q라

고 발음하며, 장치가 인터럽트 신호를 마이크로프로세서로 전송할 수 있는 하드웨

어 회선입니다. PCI IRQ 핀은 일반적으로 다음과 같이 PCI 버스 핀에 연결됩니다.

순서

1 2 3 4

슬롯

PCI 1 INT A# INT B# INT C# INT D#

41

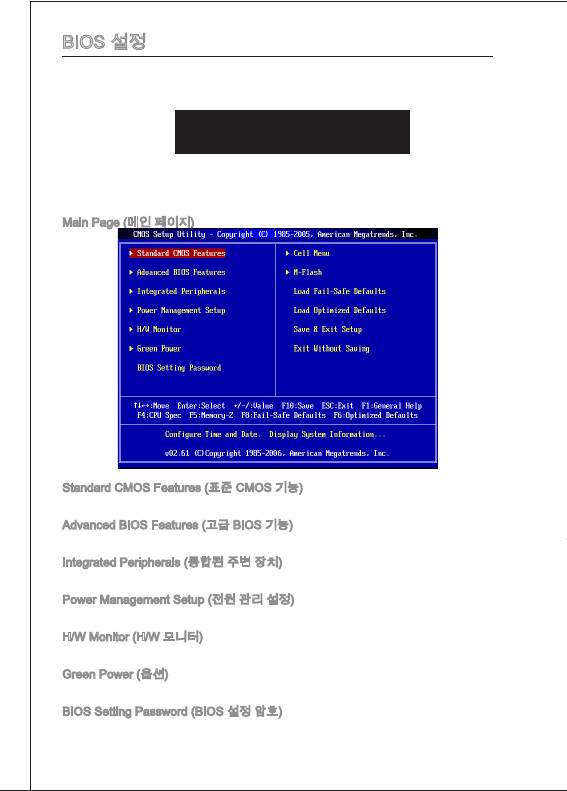

BIOS 설정

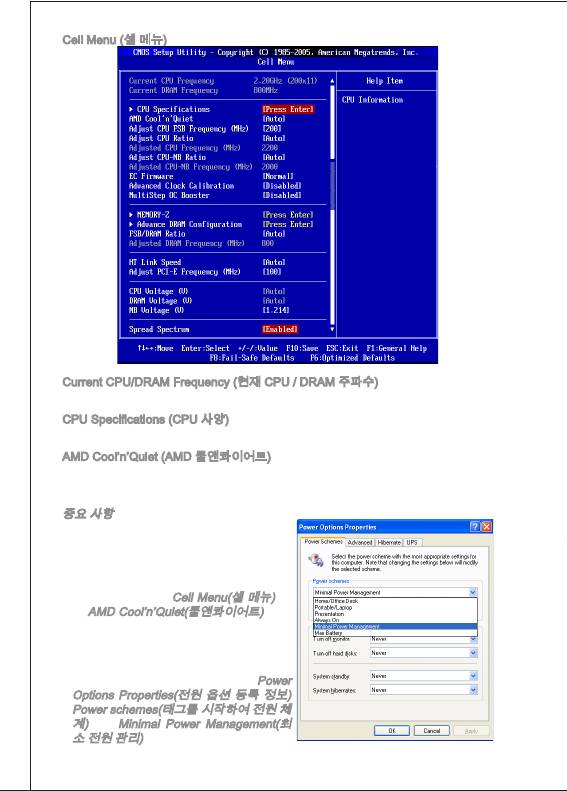

Cell Menu (셀 메뉴)

컴퓨터를 켜면 시스템이 POST(Power On Self Test) 프로세스를 시작합니다. 화면

이 메뉴를 사용하여 주파수/전압 제어의 설정을 지정합니다.

에 아래의 메시지가 표시되면, <DEL> 키를 눌러 설정을 시작합니다.

M-Flash (M-플래시)

이 메뉴를 사용하여 스토리지 드라이브에서 BIOS를 읽거나 플래시합니다 (FAT/

Press DEL to enter SETUP

FAT32 포맷 전용).

(DEL을 눌러 설정을 시작합니다.)

Load Fail-Safe Defaults (장애시 안전 기본값 로드)

이 메뉴를 사용하여 시스템 작동에 대한 공장 설정값인 BIOS 기본값을 로드합니

사용자가 응답하거나 설정을 입력하기 전에 메시지가 표시되면, 시스템을 껐다가

다.

다시 켜거나 리셋(RESET) 버튼을 눌러 다시 시작합니다. 또한 <Ctrl>, <Alt> 및

<Delete> 키를 동시에 눌러 시스템을 다시 시작할 수도 있습니다.

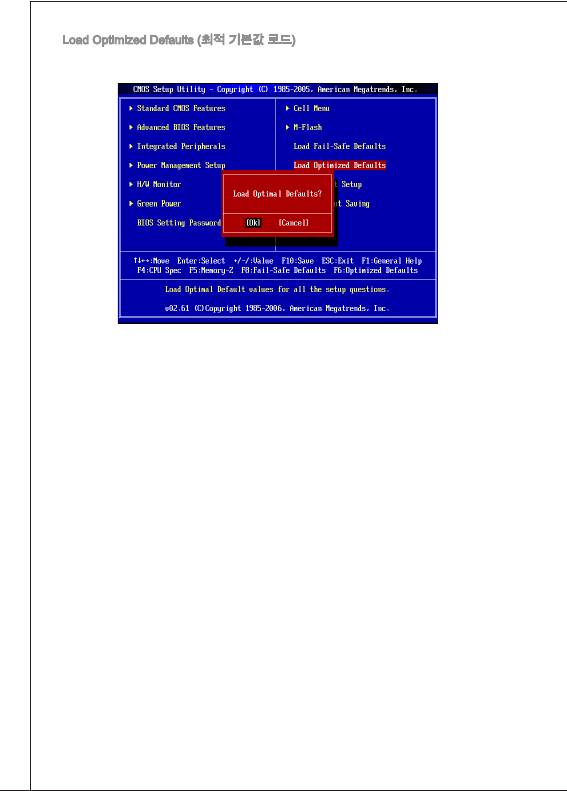

Load Optimized Defaults (최적 기본값 로드)

이 메뉴를 사용하여 안정적인 시스템 성능 작동을 위해 공장 기본 설정값을 BIOS에

Main Page (메인 페이지)

로드합니다.

Save & Exit Setup (저장 및 설정 종료)

CMOS에 변경 사항을 저장하고 설정을 종료합니다.

Exit Without Saving (저장하지 않고 종료)

모든 변경 사항을 취소하고 설정을 종료합니다.

Standard CMOS Features (표준 CMOS 기능)

이 메뉴를 사용하여 시간, 날짜 등과 같은 기본 시스템 구성을 처리합니다.

Advanced BIOS Features (고급 BIOS 기능)

이 메뉴를 사용하여 특별 고급 기능의 항목을 설정합니다.

Integrated Peripherals (통합된 주변 장치)

이 메뉴를 사용하여 통합된 주변 장치의 설정을 지정합니다.

Power Management Setup (전원 관리 설정)

이 메뉴를 사용하여 전원 관리의 설정을 지정합니다.

H/W Monitor (H/W 모니터)

이 항목은 CPU와 팬의 상태, 전반적인 시스템 상태에 대한 경고를 표시합니다.

Green Power (옵션)

이 메뉴를 사용하여 전원 위상을 지정합니다.

BIOS Setting Password (BIOS 설정 암호)

이 메뉴를 사용하여 BIOS 설정 암호를 설정합니다.

42

MS-7623

BIOS 설정

Cell Menu (셀 메뉴)

컴퓨터를 켜면 시스템이 POST(Power On Self Test) 프로세스를 시작합니다. 화면

이 메뉴를 사용하여 주파수/전압 제어의 설정을 지정합니다.

에 아래의 메시지가 표시되면, <DEL> 키를 눌러 설정을 시작합니다.

M-Flash (M-플래시)

이 메뉴를 사용하여 스토리지 드라이브에서 BIOS를 읽거나 플래시합니다 (FAT/

Press DEL to enter SETUP

FAT32 포맷 전용).

(DEL을 눌러 설정을 시작합니다.)

Load Fail-Safe Defaults (장애시 안전 기본값 로드)

이 메뉴를 사용하여 시스템 작동에 대한 공장 설정값인 BIOS 기본값을 로드합니

사용자가 응답하거나 설정을 입력하기 전에 메시지가 표시되면, 시스템을 껐다가

다.

다시 켜거나 리셋(RESET) 버튼을 눌러 다시 시작합니다. 또한 <Ctrl>, <Alt> 및

<Delete> 키를 동시에 눌러 시스템을 다시 시작할 수도 있습니다.

Load Optimized Defaults (최적 기본값 로드)

이 메뉴를 사용하여 안정적인 시스템 성능 작동을 위해 공장 기본 설정값을 BIOS에

Main Page (메인 페이지)

로드합니다.

Save & Exit Setup (저장 및 설정 종료)

CMOS에 변경 사항을 저장하고 설정을 종료합니다.

Exit Without Saving (저장하지 않고 종료)

모든 변경 사항을 취소하고 설정을 종료합니다.

Standard CMOS Features (표준 CMOS 기능)

이 메뉴를 사용하여 시간, 날짜 등과 같은 기본 시스템 구성을 처리합니다.

Advanced BIOS Features (고급 BIOS 기능)

이 메뉴를 사용하여 특별 고급 기능의 항목을 설정합니다.

Integrated Peripherals (통합된 주변 장치)

이 메뉴를 사용하여 통합된 주변 장치의 설정을 지정합니다.

Power Management Setup (전원 관리 설정)

이 메뉴를 사용하여 전원 관리의 설정을 지정합니다.

H/W Monitor (H/W 모니터)

이 항목은 CPU와 팬의 상태, 전반적인 시스템 상태에 대한 경고를 표시합니다.

Green Power (옵션)

이 메뉴를 사용하여 전원 위상을 지정합니다.

BIOS Setting Password (BIOS 설정 암호)

이 메뉴를 사용하여 BIOS 설정 암호를 설정합니다.

43

Cell Menu (셀 메뉴)

Adjust CPU FSB Frequency (CPU FSB 주파수 조정) (MHz)

이 항목에서 CPU FSB 주파수를 조정할 수 있습니다.

Adjust CPU Ratio (CPU 비율 조정)

이 항목을 사용하여 CPU 클럭 배율 (비율) 을 조정할 수 있습니다. 이 필드는 프로

세서가 이 기능을 지원할 경우에만 사용할 수 있습니다.

Adjusted CPU Frequency (조정된 CPU 주파수) (MHz)

이 항목은 조정된 CPU 주파수를 표시합니다. 읽기 전용입니다.

Adjust CPU-NB Ratio (CPU-NB 비율 조정)

이 항목은 사용하여 CPU-NB 비율을 조정할 수 있습니다.

Adjusted CPU-NB Frequency (조정된 CPU-NB 주파수) (MHz)

이 항목은 조정된 CPU-NB 주파수를 표시합니다. 읽기 전용입니다.

EC Firmware (EC 펌웨어)

이 항목을 사용하여 Advanced Clock Calibration(고급 클록 교정)을 위해 EC Firm-

ware를 선택할 수 있습니다. 추가 코어를 잠금 해제하기 위해 이 항목을 [Special(특

별)]으로 설정하고 나서 Advanced Clock Calibration(고급 클록 교정)을 [Auto(자

동)]으로 설정하면 프로세서 코어를 활성화할 수 있습니다.

Advanced Clock Calibration (고급 클록 교정)

이 항목은 오버클로킹에 사용됩니다. [Enabled(사용)]로 설정하면 CPU 속도를 더

높게설정할 수 있습니다. 이 필드는 프로세서가 이 기능을 지원할 경우에만 사용

할 수 있습니다.

Current CPU/DRAM Frequency (현재 CPU / DRAM 주파수)

MultiStep OC Booster (MultiStep OC 부스터)

CPU과 메모리의 현재 주파수를 표시합니다. 읽기 전용입니다.

이 항목은 오버클록킹으로 인해 BIOS가 깨지는 것을 막는 데 사용됩니다. [Dis-

abled(사용 안함)]으로 서정하여 이 항목을 비활성화하면 POST 동안 OC 성정을 적

CPU Specications (CPU 사양)

용합니다. [Mode 1(모드 1)] POST 작업 시 부분 OC를 적용한 다음 OS 로드 시 전체

<Enter>를 눌러 하위 메뉴를 시작하고 설치된 CPU 정보를 표시합니다.

OC를 적용합니다. [Mode 2(모드 2)] OS를 로드한 다음 OC 설정을 적용합니다.

AMD Cool’n’Quiet (AMD 쿨앤콰이어트)

MEMORY-Z (메모리 -Z)

쿨앤콰이어트 기술은 CPU 속도와 소비 전력을 효과적이고 동적으로 낮출 수 있

<Enter>를 눌러 하위 메뉴를 시작합니다. DIMM 목록에서 항목 하나를 선태하여 들

습니다.

어가고 메모리 SPD 정보를 읽습니다.

중요 사항

Advance DRAM Conguration (고급 DRAM 구성)

쿨앤콰이어트 기능이 활성화되고 제대로 작

<Enter>를 눌러 하위 메뉴를 시작합니다.

동하는지 확인하려면, 다음을 이중으로 확

DRAM Timing Mode (DRAM 타이밍 모드)

인해야 합니다

:

DRAM 모듈의 SPD (시리얼 존재 감지) EEPROM에 의해 DRAM 타이밍을 제

*

BIOS

설정을 실행하고

Cell Menu(셀 메

어하는지 어떤지 선택합니다. [Auto By SPD]으로 설정하면 SPD 구성을 기준으

뉴)

를 선택합니다

. Cell Menu(셀 메뉴)

에

로 하는 BIOS 에 의해 DRAM 타이밍 및 다음 관련 항목을 판별할 수 있습니다.

서

AMD Cool’n’Quiet(쿨앤콰이어트)

를 찾

[Manual(수동)]으로 설정하면 사용자가 DRAM 타이밍 및 다음 관련 항목을 수동

아 이 항목을

“

Enabled

(

사용

)”

으로 설정합

으로 설성할 수 있습니다.

니다

.

CAS Latency (CL) (CAS 대기 시간 (CL))

*

Windows

를 시작하여

[

시작

]-> [

설정

]->[

제

DRAM 타이밍 모드가 [Manual(수동)]으로 설정되어 있으면, 이 필드를 조정할 수

어판

]->[

전원 옵션

]

을 선택합니다.

Power

있습니다.이렇게 되면 SDRAM이 읽기 명령을 받아서 이 명령을 시작하기 전에

Options Properties(전원 옵션 등록 정보)

(클록 사이클의) 타이밍 지연을 결정하는 CAS 대기 시간을 제어합니다.

Power schemes(태그를 시작하여 전원 체

TRCD

계)

에서

Minimal Power Management(최

RAM 타이밍 모드가 [Manual(수동)]으로 설정되어 있으면, 이 필드를 조정할 수

소 전원 관리)

를 선택합니다

.

있습니다. DRAM이 재충전되면 행과 열이 따로 분리됩니다. 이 설정 항목을 사

44

MS-7623

Cell Menu (셀 메뉴)

Adjust CPU FSB Frequency (CPU FSB 주파수 조정) (MHz)

이 항목에서 CPU FSB 주파수를 조정할 수 있습니다.

Adjust CPU Ratio (CPU 비율 조정)

이 항목을 사용하여 CPU 클럭 배율 (비율) 을 조정할 수 있습니다. 이 필드는 프로

세서가 이 기능을 지원할 경우에만 사용할 수 있습니다.

Adjusted CPU Frequency (조정된 CPU 주파수) (MHz)

이 항목은 조정된 CPU 주파수를 표시합니다. 읽기 전용입니다.

Adjust CPU-NB Ratio (CPU-NB 비율 조정)

이 항목은 사용하여 CPU-NB 비율을 조정할 수 있습니다.

Adjusted CPU-NB Frequency (조정된 CPU-NB 주파수) (MHz)

이 항목은 조정된 CPU-NB 주파수를 표시합니다. 읽기 전용입니다.

EC Firmware (EC 펌웨어)

이 항목을 사용하여 Advanced Clock Calibration(고급 클록 교정)을 위해 EC Firm-

ware를 선택할 수 있습니다. 추가 코어를 잠금 해제하기 위해 이 항목을 [Special(특

별)]으로 설정하고 나서 Advanced Clock Calibration(고급 클록 교정)을 [Auto(자

동)]으로 설정하면 프로세서 코어를 활성화할 수 있습니다.

Advanced Clock Calibration (고급 클록 교정)

이 항목은 오버클로킹에 사용됩니다. [Enabled(사용)]로 설정하면 CPU 속도를 더

높게설정할 수 있습니다. 이 필드는 프로세서가 이 기능을 지원할 경우에만 사용

할 수 있습니다.

Current CPU/DRAM Frequency (현재 CPU / DRAM 주파수)

MultiStep OC Booster (MultiStep OC 부스터)

CPU과 메모리의 현재 주파수를 표시합니다. 읽기 전용입니다.

이 항목은 오버클록킹으로 인해 BIOS가 깨지는 것을 막는 데 사용됩니다. [Dis-

abled(사용 안함)]으로 서정하여 이 항목을 비활성화하면 POST 동안 OC 성정을 적

CPU Specications (CPU 사양)

용합니다. [Mode 1(모드 1)] POST 작업 시 부분 OC를 적용한 다음 OS 로드 시 전체

<Enter>를 눌러 하위 메뉴를 시작하고 설치된 CPU 정보를 표시합니다.

OC를 적용합니다. [Mode 2(모드 2)] OS를 로드한 다음 OC 설정을 적용합니다.

AMD Cool’n’Quiet (AMD 쿨앤콰이어트)

MEMORY-Z (메모리 -Z)

쿨앤콰이어트 기술은 CPU 속도와 소비 전력을 효과적이고 동적으로 낮출 수 있

<Enter>를 눌러 하위 메뉴를 시작합니다. DIMM 목록에서 항목 하나를 선태하여 들

습니다.

어가고 메모리 SPD 정보를 읽습니다.

중요 사항

Advance DRAM Conguration (고급 DRAM 구성)

쿨앤콰이어트 기능이 활성화되고 제대로 작

<Enter>를 눌러 하위 메뉴를 시작합니다.

동하는지 확인하려면, 다음을 이중으로 확

DRAM Timing Mode (DRAM 타이밍 모드)

인해야 합니다

:

DRAM 모듈의 SPD (시리얼 존재 감지) EEPROM에 의해 DRAM 타이밍을 제

*

BIOS

설정을 실행하고

Cell Menu(셀 메

어하는지 어떤지 선택합니다. [Auto By SPD]으로 설정하면 SPD 구성을 기준으

뉴)

를 선택합니다

. Cell Menu(셀 메뉴)

에

로 하는 BIOS 에 의해 DRAM 타이밍 및 다음 관련 항목을 판별할 수 있습니다.

서

AMD Cool’n’Quiet(쿨앤콰이어트)

를 찾

[Manual(수동)]으로 설정하면 사용자가 DRAM 타이밍 및 다음 관련 항목을 수동

)”

아 이 항목을

“

Enabled

(

사용

으로 설정합

으로 설성할 수 있습니다.

니다

.

CAS Latency (CL) (CAS 대기 시간 (CL))

Windows

를 시작하여

[

시작

]-> [

설정

*

제

]->[

DRAM 타이밍 모드가 [Manual(수동)]으로 설정되어 있으면, 이 필드를 조정할 수

]

Power

을 선택합니다.

전원 옵션

]->[

어판

있습니다.이렇게 되면 SDRAM이 읽기 명령을 받아서 이 명령을 시작하기 전에

Options Properties(전원 옵션 등록 정보)

(클록 사이클의) 타이밍 지연을 결정하는 CAS 대기 시간을 제어합니다.

Power schemes(태그를 시작하여 전원 체

TRCD

Minimal Power Management(최

에서

계)

RAM 타이밍 모드가 [Manual(수동)]으로 설정되어 있으면, 이 필드를 조정할 수

.

를 선택합니다

소 전원 관리)

있습니다. DRAM이 재충전되면 행과 열이 따로 분리됩니다. 이 설정 항목을 사

45

용하면 RAS(열 주소)에서 CAS(행 주소)로의 변환 타이밍을 결정할 수 있습니다.

FSB/DRAM Ratio (FSB/DRAM 비율)

클록 사이클이 짧을수록 DRAM 성능이 빨라집니다.

이 항목을 사용하면 FSB/DRAM 비율을 설정할 수 있습니다.

TRP

Adjusted DRAM Frequency (조정된 DRAM 주파수) (MHz)

DRAM 타이밍 모드가 [Manual(수동)]으로 설정되어 있으면, 이 필드를 조정할

이 항목은 조정된 DDR 메모리 주파수를 표시합니다. 읽기 전용입니다.

수 있습니다. 이 항목은 사전에 충전할 수 있는 RAS 사이클 수를 제어합니다.

HT Link Speed (HT 링크 속도)

DRAM 재충전 이전에 RAS가 충전 시간을 충분히 갖지 못할 경우, 충전이 불충

이 항목을 사용하면 하이퍼 전송 링크 속도를 설정할 수 있습니다. [자동(Auto)] 으

분해서 DRAM이 데이터를 보존하지 못할 수 있습니다. 이 항목은 시스템에 동기

로 설정하면 시스템은 HT 링크 속도를 자동으로 감지합니다.

화 DRAM이 설치된경우에만 적용됩니다.

Adjust PCI-E Frequency (PCI-E 주파수 조정) (MHz)

TRAS

이 항목을 사용하여 PCI-E 주파수(in MHz)를 설정할 수 있습니다.

DRAM 타이밍 모드가 [Manual(수동)]으로 설정되어 있으면, 이 설정은 RAS가

메모리 셀로부터 읽거나 메모리 셀에 쓰는 데 걸리는 시간을 결정합니다.

CPU Voltage (V) (CPU 전압 (V))

이 항목은 CPU 전압 조정에 사용됩니다.

TRTP

DRAM 타이밍 모드가 [Manual(수동)]으로 설정되어 있으면, 이 설정은 읽기와 선

DRAM Voltage (V) (DRAM 전압 (V))

충전 명령 사이의 시간 간격을 제어합니다.

이 항목은 메모리 전압 조정에 사용됩니다.

TRC

NB Voltage (V) (NB 전압 (V))

DRAM 타이밍 모드가 [Manual(수동)]으로 설정되어 있으면, 이 필드를 조정할

이 항목은 노스 브릿지 전압 조정에 사용됩니다.

수 있습니다. 행 사이클 시간은 메모리 행이 행 활성화에서 현재 행의 사전 충

Spread Spectrum (대역 확산)

전에 이르기까지 전체 사이클을 완료하는 데 필요한 클록 사이클의 최소 수를

마더 보드의 클록 생성기가 펄스화되면 펄스의 극치값(스파이크)이 전자파 장애

결정합니다.

를 일으킵니다. 대역 확산 기능은 펄스 조절로 생성된 EMI를 줄여줌으로써 그 결

TWR

과 펄스의 스파이크가 평탄한 곡선으로 줄어듭니다. EMI 문제가 발생하지 않을 경

DRAM 타이밍 모드가 [Manual(수동)]으로 설정되어 있으면, 이 필드를 조정할 수

우 최적의 시스템 안정성 및 성능을 위해 사용 안함으로 설정합니다. 그러나 EMI로

있습니다. 유효한 쓰기 작업의 완료 후 현재 뱅크를 사전 충전할 수 있을 때까지

인해 문제가 발생할 경우 EMI 감소를 사용으로 설정하십시오. 사소한 지터조차도

경과해야 하는 지연(클럭 사이클의)을 지정합니다. 이지연은 사전 충전이 발생하

클록 속도를 일시적으로 상승시키면 오버클로킹한 프로세스를 고정시키는 원인

기 전에 쓰기 버퍼의 데이터를 메모리 셀에 쓸 수 있도록 하는 데 필요합니다.

이 될 수 있으므로 오버클로킹을 진행하는 동안 대역 확산을 반드시 사용 안함으

로 설정해야 합니다.

TRRD

DRAM 타이밍 모드가 [Manual(수동)]으로 설정되어 있으면, 이 필드를 조정할 수

중요 사항

있습니다. 다른 뱅크의 active-to-active 지연을 지정합니다.

*

EMI 문제가 발생하지 않을 경우 최적의 시스템 안정성 및 성능을 위해 [사용 안

TWTR

함]으로 설정합니다. 그러나 EMI로 인해 문제가 발생할 경우 EMI 감소를 위해 대

DRAM 타이밍 모드가 [Manual(수동)]으로 설정되어 있으면, 이 필드를 조정할

역 확산 값을 선택하십시오.

수 있습니다. 이 항목은 읽기 명령지연에 데이터 쓰기(Write Data In to Read

Command Delay) 메모리 타밍을 제어합니다. 이 항목이 DDR 장치의 동일한 내

*

대역 확산 값이 클수록 EMI는 감소되지만 시스템의 안정성은 저하됩니다. 가장

부 뱅크에 대한 유효한 최종 쓰기 작업과 다음 읽기 명령 사이에 발생하는 클럭

적합한 대역 확산 값은 해당 지역의 EMI 규정을 참조하십시오.

사이클의 최소 수를 구성합니다.

*

사소한 지터조차도 클록 속도를 일시적으로 상승시키면 오버클로킹한 프로세스

1T/2T Memory Timing (1T/2T 메모리 타이밍)

를 고정시키는 원인이 될 수 있으므로 오버클로킹을 진행하는 동안 대역 확산을

DRAM 타이밍 모드가 [Manual(수동)]으로 설정되어 있으면, 이 필드를 조정할

반드시 사용 안함으로 설정해야 합니다.

수 있습니다. 이 필드가 SDRAM 명령 대기 시간을 제어합니다. [1T]를 선택하면

SDRAM 신호 컨트롤러가 1T(T=클럭 사이클) 속도로 실행됩니다. [2T]를 선택하

면 SDRAM 신호 컨트롤러가 2T 속도로 실행됩니다.

SoftWare Memory Hole (소프트웨어 메모리 홀)

DRAM 타이밍 모드가 [Manual(수동)]으로 설정되어 있으면, 이 필드를 조정할

수 있습니다. 이 필드에서는 소프트웨어 메모리 홀을 활성화/비활성화할 수 있

습니다.

46

MS-7623

용하면 RAS(열 주소)에서 CAS(행 주소)로의 변환 타이밍을 결정할 수 있습니다.

FSB/DRAM Ratio (FSB/DRAM 비율)

클록 사이클이 짧을수록 DRAM 성능이 빨라집니다.

이 항목을 사용하면 FSB/DRAM 비율을 설정할 수 있습니다.

TRP

Adjusted DRAM Frequency (조정된 DRAM 주파수) (MHz)

DRAM 타이밍 모드가 [Manual(수동)]으로 설정되어 있으면, 이 필드를 조정할

이 항목은 조정된 DDR 메모리 주파수를 표시합니다. 읽기 전용입니다.

수 있습니다. 이 항목은 사전에 충전할 수 있는 RAS 사이클 수를 제어합니다.

HT Link Speed (HT 링크 속도)

DRAM 재충전 이전에 RAS가 충전 시간을 충분히 갖지 못할 경우, 충전이 불충

이 항목을 사용하면 하이퍼 전송 링크 속도를 설정할 수 있습니다. [자동(Auto)] 으

분해서 DRAM이 데이터를 보존하지 못할 수 있습니다. 이 항목은 시스템에 동기

로 설정하면 시스템은 HT 링크 속도를 자동으로 감지합니다.

화 DRAM이 설치된경우에만 적용됩니다.

Adjust PCI-E Frequency (PCI-E 주파수 조정) (MHz)

TRAS

이 항목을 사용하여 PCI-E 주파수(in MHz)를 설정할 수 있습니다.

DRAM 타이밍 모드가 [Manual(수동)]으로 설정되어 있으면, 이 설정은 RAS가

메모리 셀로부터 읽거나 메모리 셀에 쓰는 데 걸리는 시간을 결정합니다.

CPU Voltage (V) (CPU 전압 (V))

이 항목은 CPU 전압 조정에 사용됩니다.

TRTP

DRAM 타이밍 모드가 [Manual(수동)]으로 설정되어 있으면, 이 설정은 읽기와 선

DRAM Voltage (V) (DRAM 전압 (V))

충전 명령 사이의 시간 간격을 제어합니다.

이 항목은 메모리 전압 조정에 사용됩니다.

TRC

NB Voltage (V) (NB 전압 (V))

DRAM 타이밍 모드가 [Manual(수동)]으로 설정되어 있으면, 이 필드를 조정할

이 항목은 노스 브릿지 전압 조정에 사용됩니다.

수 있습니다. 행 사이클 시간은 메모리 행이 행 활성화에서 현재 행의 사전 충

Spread Spectrum (대역 확산)

전에 이르기까지 전체 사이클을 완료하는 데 필요한 클록 사이클의 최소 수를

마더 보드의 클록 생성기가 펄스화되면 펄스의 극치값(스파이크)이 전자파 장애

결정합니다.

를 일으킵니다. 대역 확산 기능은 펄스 조절로 생성된 EMI를 줄여줌으로써 그 결

TWR

과 펄스의 스파이크가 평탄한 곡선으로 줄어듭니다. EMI 문제가 발생하지 않을 경

DRAM 타이밍 모드가 [Manual(수동)]으로 설정되어 있으면, 이 필드를 조정할 수

우 최적의 시스템 안정성 및 성능을 위해 사용 안함으로 설정합니다. 그러나 EMI로

있습니다. 유효한 쓰기 작업의 완료 후 현재 뱅크를 사전 충전할 수 있을 때까지

인해 문제가 발생할 경우 EMI 감소를 사용으로 설정하십시오. 사소한 지터조차도

경과해야 하는 지연(클럭 사이클의)을 지정합니다. 이지연은 사전 충전이 발생하

클록 속도를 일시적으로 상승시키면 오버클로킹한 프로세스를 고정시키는 원인

기 전에 쓰기 버퍼의 데이터를 메모리 셀에 쓸 수 있도록 하는 데 필요합니다.

이 될 수 있으므로 오버클로킹을 진행하는 동안 대역 확산을 반드시 사용 안함으

로 설정해야 합니다.

TRRD

DRAM 타이밍 모드가 [Manual(수동)]으로 설정되어 있으면, 이 필드를 조정할 수

중요 사항

있습니다. 다른 뱅크의 active-to-active 지연을 지정합니다.

*

EMI 문제가 발생하지 않을 경우 최적의 시스템 안정성 및 성능을 위해 [사용 안

TWTR

함]으로 설정합니다. 그러나 EMI로 인해 문제가 발생할 경우 EMI 감소를 위해 대

DRAM 타이밍 모드가 [Manual(수동)]으로 설정되어 있으면, 이 필드를 조정할

역 확산 값을 선택하십시오.

수 있습니다. 이 항목은 읽기 명령지연에 데이터 쓰기(Write Data In to Read

Command Delay) 메모리 타밍을 제어합니다. 이 항목이 DDR 장치의 동일한 내

*

대역 확산 값이 클수록 EMI는 감소되지만 시스템의 안정성은 저하됩니다. 가장

부 뱅크에 대한 유효한 최종 쓰기 작업과 다음 읽기 명령 사이에 발생하는 클럭

적합한 대역 확산 값은 해당 지역의 EMI 규정을 참조하십시오.

사이클의 최소 수를 구성합니다.

*

사소한 지터조차도 클록 속도를 일시적으로 상승시키면 오버클로킹한 프로세스

1T/2T Memory Timing (1T/2T 메모리 타이밍)

를 고정시키는 원인이 될 수 있으므로 오버클로킹을 진행하는 동안 대역 확산을

DRAM 타이밍 모드가 [Manual(수동)]으로 설정되어 있으면, 이 필드를 조정할

반드시 사용 안함으로 설정해야 합니다.

수 있습니다. 이 필드가 SDRAM 명령 대기 시간을 제어합니다. [1T]를 선택하면

SDRAM 신호 컨트롤러가 1T(T=클럭 사이클) 속도로 실행됩니다. [2T]를 선택하

면 SDRAM 신호 컨트롤러가 2T 속도로 실행됩니다.

SoftWare Memory Hole (소프트웨어 메모리 홀)

DRAM 타이밍 모드가 [Manual(수동)]으로 설정되어 있으면, 이 필드를 조정할

수 있습니다. 이 필드에서는 소프트웨어 메모리 홀을 활성화/비활성화할 수 있

습니다.

47

Load Optimized Defaults (최적 기본값 로드)

메인보드 안정적인 성능을 위해 메인보드 제조업체가 제공한 기본값을 로드할 수

있습니다.

48

LED1 (Optional)

Top : mouse

CP UFAN

Bo tto m:keybo ard

CO M Por t

JLPT1

SOCKET AM3

VG A port

JP WR1

USB por ts

JP WR2

Top: L AN Jack

Bo tto m: US B port s

IDE 1

SYSFAN 1

T:Li ne- In

M: Lin e- Ou t

JC OM1

AMD

DI MM1

DI MM2

B: MIC -In t

JCI1

T: RS-Out (Optional)

740G/ 760G

M: CS-Out (Optional)

(Optio nal)

PCI_E1

B: SS-Out (Optional)

PCI_E2

PCI_E3

+

AM D

BATT

SB710

SATA5_ 6

ON

OC_SW1

(Optional)

12

PCI1

SATA3_ 4

JFP2

JC D1

JB AT1

JA UD1

JFP1

JS P1

JT PM1 JU SB1 JU SB2

SATA1

SATA2

FD D1

12 . +3.3

11

10 . +12V

.+ 1 2V

9. 5 VSB

8. P W

V

7

6. + 5

.G r ound

5

R O

4. + 5

.G r ound

V

3

K

2. + 3.3

.G r ound

V

1. + 3.3

24 . Groun d

V

23 . +5

V

22 . +5

21 . +5

20 . Res

V

19 . Groun d

V

18 . Groun d

V

17 . Groun d

16 . PS-ON

15 . Groun d

14 . -12V

13 . +3.3

#

V

1

2

.G r ound

.G r ound

3. + 12V

4. + 12V

3

2

.

G

.

1

S

r

.

V

P

o

u

D

n

C

C

I

F

d

1

2

.

L

.

3

G

4

.

G

r

o

.

R

r

u

o

n

u

d

n

d

P

ow e r

P

S

ow e r

wi t ch

10 . No

LE

Pi

D

8.

n

6.

-

4.

+

2.

-

+

9. R eserv e

7.

5.

+

3.

-

1.

-

+

Re s et

d

HD D L E

S

wi t ch

D

S

peaker

8.

Buzzer

6.

+

4.

-

2.

+

-

7.No

5.Power

3.Suspend

Pi

1

.Ground

n

LE

D

LE

D

1

0

8

.

.

N

6

C

o

.

T

P

4

D

S

.

S

i

n

2

D

R

.

T

S

R

I

N

9

7

.

R

5

.

R

I

3

.

G

T

1

.

S

r

S

.

D

O

o

u

C

U

n

T

d

D

1

2

.

G

3

.

r

4

.

+

S

1

o

.

e

2

u

C

V

n

o

n

d

n

s

t

o

r

r

o

l

1

2

.

G

3

.

+

r

.

N

1

o

o

2

u

V

n

U

d

s

e

3

2

.

G

.

1

S

r

.

V

P

o

u

D

n

C

C

I

F

d

1

2

.

L

.

3

G

4

.

G

r

o

.

R

r

u

o

n

u

d

n

d

P

ow e r

P

S

wi t ch

10 . No

ow e r

LE

Pi

D

8.

n

6.

-

4.

+

2.

-

+

9. R eserv e

7.

5.

+

3.

-

1.

-

+

Re s et

d

HD D

S

wi t ch

LE

D

S

peaker

8.

Buzzer

6.

+

4.

-

2.

+

-

7.No

5.Power

3.Suspend

Pi

1

.Ground

n

LE

D

LE

D

1

0

8

.

.

N

6

C

o

.

T

P

4

D

S

.

S

i

n

2

D

R

.

T

S

R

I

N

9

7

.

R

5

.

R

I

3

.

G

T

1

.

S

r

S

.

D

O

o

u

C

U

n

T

d

D

1

G

.

2

r

3

.

1

4

S

.

+

o

u

V

n

d

e

2

n

.

C

s

o

o

n

r

r

t

o

l

1

G

.

2

+

r

3

.

N

.

1

o

2

u

d

V

n

o

U

s

e

2

1

.

G

.

C

r

o

I

N

u

n

T

d

R

U

1

1

1

2

2

6

2

4

.

N

2

.

G

o

2

r

P

0

.

G

o

i

1

n

8

.

G

r

o

u

n

1

.

r

6

G

o

u

n

d

1

.

G

r

u

4

o

n

d

1

.

r

u

o

n

d

G

1

2

.

r

u

d

0

G

o

n

8

.

G

r

o

u

d

n

6

.

L

r

u

d

.

P

P

o

n

4

d

I

T

u

.

E

N

_

n

2

S

d

2

R

I

5

.

A

R

T

L

#

I

2

.

S

F

#

N

2

3

L

D

#

1

.

P

C

#

1

9

.

B

E

T

1

.

A

U

1

7

.

P

C

S

1

5

.

K

Y

P

R

#

1

3

.

N

1

P

R

9

.

N

D

P

R

N

D

7

7

.

P

R

D

6

5

.

P

R

N

N

D

5

3

.

P

R

D

4

1

.

P

R

N

N

D

3

.

R

R

2

S

N

D

D

1

T

B

0

#

1

0

8

.

6

.

H

N

e

.

o

a

4

M

.

I

P

d

P

C

i

P

2

n

h

.

G

R

E

D

o

r

n

o

S

e

t

u

E

e

e

n

N

c

D

d

t

i

e

C

o

t

E

n

e

c

#

t

i

o

n

9

7

.

H

5

.

S

e

a

3

.

H

E

d

N

P

1

.

M

e

a

S

.

M

I

C

d

E

h

o

n

I

_

C

R

P

h

S

e

o

E

L

L

n

N

e

D

R

1

0

8

.

.

U

6

G

S

.

U

r

o

B

4

.

U

S

u

O

2

C

S

B

n

.

d

V

C

B

1

+

C

1

-

9

7

.

N

5

.

G

o

P

3

.

U

r

o

i

n

1

.

U

S

u

.

S

B

n

V

B

0

d

C

C

0

+

-

1

1

4

.

1

2

G

0

.

G

r

o

8

.

r

u

6

.

N

o

5

o

u

n

d

.

n

4

S

V

e

P

P

i

d

.

o

n

2

3

r

i

w

.

.

a

3

3

V

V

l

I

e

r

S

P

R

Q

t

o

a

w

n

e

d

r

b

y

p

o

w

e

1

r

1

3

1

.

L

9

.

L

P

P

C

7

.

L

5

.

C

F

L

P

C

a

r

.

P

a

3

L

P

C

a

d

m

.

L

a

d

d

d

r

e

1

.

C

e

L

P

P

C

a

d

d

r

e

s

C

s

R

d

d

r

e

s

s

&

C

e

r

e

s

s

&

d

l

s

e

o

s

a

c

t

s

&

d

a

t

k

&

d

a

t

a

a

d

t

p

a

p

i

a

n

t

a

p

i

n

3

i

n

2

p

i

n

1

0

2

1

.

G

.

C

r

o

I

N

u

n

T

d

R

U

1

1

1

2

2

6

2

4

.

N

2

.

G

o

2

r

P

0

.

G

o

i

1

n

8

.

G

r

o

u

n

1

.

r

6

G

o

u

n

d

1

.

G

r

u

4

o

n

d

1

.

r

u

o

n

d

G

1

2

.

r

u

d

0

G

o

n

8

.

G

r

o

u

d

n

6

.

L

r

u

d

.

P

P

o

n

4

d

I

T

u

.

E

N

_

n

2

S

d

2

R

I

5

.

A

R

T

L

#

I

2

.

S

F

#

N

2

3

L

D

#

1

.

P

C

#

1

9

.

B

E

T

1

.

A

U

1

7

.

P

C

S

1

5

.

K

Y

P

R

#

1

3

.

N

1

P

R

9

.

N

D

P

R

N

D

7

7

.

P

R

D

6

5

.

P

R

N

N

D

5

3

.

P

R

D

4

1

.

P

R

N

N

D

3

.

R

R

2

S

N

D

D

1

T

B

0

#

1

0

8

H

.

a

N

.

e

6

4

d

P

M

.

o

P

.

C

I

P

h

i

o

2

n

n

G

D

.

R

e

E

t

e

S

o

r

e

c

n

u

D

E

N

d

t

e

t

n

E

e

i

o

C

t

c

o

#

i

n

9

.

H

e

7

5

.

.

a

S

P

3

d

E

N

H

1

.

e

M

S

d

C

I

a

E

h

.

o

_

n

M

C

I

R

P

L

h

e

S

o

E

n

L

N

e

D

R

1

0

8

.

.

U

G

S

r

6

o

.

U

B

u

4

.

n

U

S

O

C

B

2

1

d

S

+

B

.

V

1

C

-

C

9

.

N

o

7

5

.

G

o

r

.

P

U

3

.

n

i

U

S

1

u

S

B

n

d

.

+

B

V

0

0

C

-

C

1

1

4

2

G

.

.

o

r

1

G

0

r

o

u

N

.

8

6

u

5

.

o

n

V

.

P

n

d

d

4

P

S

o

e

n

i

.

w

3

2

r

i

.

a

.

3

3

V

l

r

I

e

V

S

R

Q

P

o

w

t

e

a

d

r

n

b

y

p

o

w

1

1

3

e

r

1

L

.

L

.

P

9

P

C

7

L

.

P

C

F

L

r

C

.

a

L

d

P

5

C

m

a

.

a

d

r

a

d

d

e

3

P

1

L

.

a

s

e

r

C

P

e

C

s

L

.

d

e

s

s

P

d

d

C

d

R

r

&

e

&

d

a

C

r

e

s

l

e

s

t

o

d

s

&

s

t

d

&

c

a

a

s

t

k

a

p

a

t

a

d

i

a

t

p

n

i

n

p

3

a

n

2

p

i

n

i

1

0